IPUs, DPUs, DLUs und mehr Wo Hardware zählt: KI mit System

Wer ernten will, muss säen — auch Künstliche Intelligenz (KI) ist da keine Ausnahme. Der Wettlauf um die schlausten KI-Anwendungen fordert hochperformante Hardware der besonderen Art. Eine CPU ist nicht alles.

Anbieter zum Thema

Lernende Algorithmen müssen präzedenzlose Datenmengen echtzeitnah bewältigen. Sie müssen in der Lage sein, in unvorhersehbaren Situationen und gleichzeitig in einem stark individualisierten Kontext intelligente Entscheidungen zu treffen. Lernfähige Backend-Technologien für KI-Anwendungen wie programmatische Werbung, autonomes Fahren oder intelligente Infrastrukturen haben hierzu den benötigten Reifegrad bereits erreicht. Was fehlt ist die geeignete Hardware.

Zum Teil auf Grund diverser Unzulänglichkeiten heutiger Hardwarearchitekturen wirft der Praxiseinsatz von KI gewaltige Herausforderungen auf. Diese werden durch das Ende des Mooreschen Gesetzes auch noch verschärft. Hinzu kommen anwendungsspezifische Beschränkungen technischer Eckdaten Cyber-physischer Systeme: der Platzbedarf, das Gewicht, der Energieverbrauch und anderes mehr.

Alleine die Gewährleistung von Cyber-Sicherheit und Datenintegrität in personenbezogenen Anwendungsszenarien gestaltet sich angesichts neuartiger Attacken wie Adversarial Learning („bösartiges Lernen“ auf der Basis von betrügerischen Daten) extrem schwierig. Konventionelle Systemarchitekturen werden den neuen Herausforderungen einfach nicht gerecht.

Das Ende von Moore’s Law und Dennards Gesetz

Seit der Erfindung integrierter Schaltkreise für konventionelle Silikon-Chips galten das Mooresche Gesetz (Moore’s Law) und Dennards Gesetz als die ultimative Richtschnur für den technischen Fortschritt der Branche. Das Mooresche Gesetz besagt, dass sich die Anzahl von Transistoren in einem integrierten Schaltkreis (bei gleichbleibenden Fertigungskosten wohlgemerkt) ungefähr alle zwei Jahre verdoppeln würde. Spätestens wenn die Bauelemente konventioneller Schaltkreise auf den so genannten Monolayer - eine einzige atomare Schicht, die sie nicht weiter unterschreiten lässt - sinken, ist das Ende der Fahnenstange erreicht.

Das Ende des Mooreschen Gesetzes rückt nahe. Die Dennardsche Skalierung ist bereits im Jahre 2005 zusammengebrochen, bestätigte vor drei Jahren Professor Christian Märtin von der Hochschule Augsburg in einem technischen Bericht („Post-Dennard Scaling and the final Years of Moore’s Law. Consequences for the Evolution of Multicore-Architectures“, siehe auch das eBook „High Performance Computing“

Dennards Gesetz besagt, dass die fortschreitende Minifizierung des grundlegenden Bauelementes in einem Schaltkreis mit einer niedrigeren Stromspannung einherginge und bei gleichbleibendem Leistungsverbrauch eine höhere Taktfrequenz erzielen ließe. Obwohl die Transistoren vorerst noch weiterhin schrumpfen, würden die Fehlerrate und damit die Fertigungskosten von CPUs aufgrund von Effekten wie Leckstrom und Schwellenspannung erstmals nicht weiter nachgeben.

Workload-spezifische Hardwarebeschleunigung

Der einzige Weg, um auch in Zukunft weiterhin an der Schraube der Leistung-zu-Leistungsaufnahme-zu-Anschaffungskosten-Variablen drehen zu können, bestünde in der Entwicklung Workload-spezifischer Hardwarebeschleuniger, meinen die Forscher der UC Berkeley in einem Bericht vom Oktober 2017 („A Berkeley View of Systems Challenges for AI“. Abhilfe versprächen das Aufkommen domänenspezifischer Hardware-Architekturen, zusammensetzbarer Infrastrukturen und Edge-Architekturen (siehe dazu auch das eBook „Edge Computing“). Denn weitere Verbesserungen ließen sich jetzt nur noch durch Innovationen in Computerarchitekturen, nicht jedoch in Verbesserungen am Halbleiterprozess, verwirklichen, so die Berkeley-Forscher.

Domain-spezifische Prozessoren können nur wenige Aufgaben erledigen, dafür aber extrem gut. Zukünftige Server würden daher „viel heterogener sein“ als jemals in der Vergangenheit. Als ein „wegweisendes Beispiel“ zitieren die Berkeley-Forscher Die „Tensor Processing Unit“ (TPU) von Google, einen anwendungsspezifischen KI-Beschleuniger in ASIC-Architektur (Application-Specific Integrated Circuits). Googles TPU führt die Inferenz-Phase tiefer neuronalen Netze 15 bis 30 mal schneller als CPUs und GPUs aus bei einer 30- bis 80fach besseren Leistung per Watt.

Die aktuelle zweite Generation der TPU liefert 45 Teraflops, ist (erstmals) fließkommafähig und unterstützt eine Bandbreite von 600 GBps per ASIC. In einer parallelen Architektur von vier TPU-Chips kommt das resultierende Modul auf eine Leistung von 180 TFLOPS; je 64 dieser Module bilden zu 256er Gruppen so genannte Chip-Pods mit einer Gesamtleistung von 11,5 PFLOPS.

ASICs bei Google und FPGAs bei Microsoft

Googles TPU mag auch noch so wegweisend sein, sie ist rein proprietär und zudem nicht kommerziell verfügbar. So müssen Googles Mitbewerber bei KI-Workloads mit Alternativen Vorlieb nehmen.

Im Gegensatz zu Google setzen sowohl Microsoft als auch Intel auf FPGAs. Microsoft bietet FPGA-basierte Compute-Instanzen als einen Azure-Dienst an. Intel ließ sich den FPGA-Anbieter Altera satte 16,7 Milliarden Dollar kosten.

ASICs (Application-Specific Integrated Circuits) und FPGAs (Field Programmable Gate Arrays) basieren auf zwei gegensätzlichen Konzepten. Bei ASICs handelt es sich um anwendungsspezifische integrierte Schaltkreise, die gemäß sehr eng definierter Design-Eckdaten gefertigt werden. Sie zeichnen sich durch sehr geringe Stückkosten aus, sind jedoch nicht veränderbar.

Im Gegensatz zu ASICs lassen sich integrierte Schaltkreise vom Typ FPGA auch nach der Inbetriebnahme im Datencenter an neue Workloads per Remote-Zugriff anpassen (siehe dazu das eBook „Das programmierbare Rechenzentrum“). Die Chip-Entwicklung von der Idee bis zum Prototypen dauert bei FPGAs nur sechs Monate; bei ASICS bis zu 18 Monate, verrät Dr. Randy Huang, FPGA Architect von Intels Programmable Solutions Group. Sowohl ASICs als auch FPGAs glänzen durch eine hohe Energie-Effizienz im Vergleich zur GPUs--Beschleunigung. GPUs (Graphic Processing Units) trumpfen wiederum mit einer hohen Maximalleistung bei Fließkommaberechnungen.

GPUnktet: die Chance beim Schopf packen

Dank ihrer massiven Parallelisierbarkeit schlagen GPUs bei KI-Anwendungen die Leistung konventioneller CPUs um Längen. So liefert Die Nvidia-GPU „Tesla“ laut Hersteller eine bis zu 27-fache Beschleunigung bei der Inferenz-Phase neuronaler Netze gegenüber einem System mit nur einer Ein-Socket-CPU.

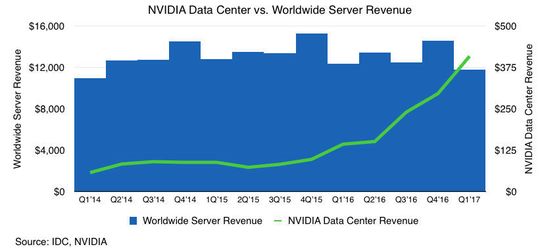

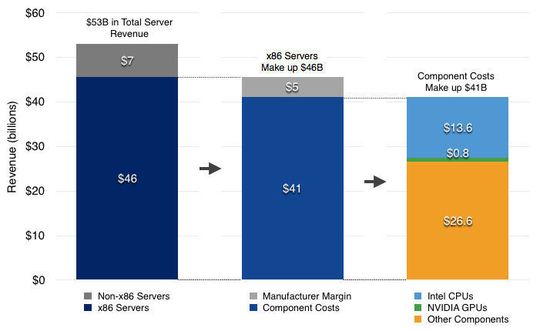

Den Markt für KI-Beschleuniger im Rechenzentrum dominiert Nvidia. Selbst Google nutzt die „Tesla P100“ und „Tesla K80“ GPUs im Rahmen der „Google Cloud Plattform“.

Die Nvidia-Umsätze mit Rechenzentren sind in den vergangenen Monaten sprunghaft gestiegen. Der GPU-Marktführer hat daraufhin eine strategische Diversifizierung seines Technologieportfolios weg von Spielen und hin zu KI — mit bemerkenswerter Ernsthaftigkeit — vorgenommen... und sich damit aber keine Freunde gemacht.

In den neuesten EULA-Lizenzbedingungen der Grafikkartentreiber verbietet Nvidia die Nutzung der kostengünstigeren „GeForce GTX“- und „Titan“-GPUs in Datencenter. Im Rechenzentrumsumfeld ist nur noch die Blockchain-Verarbeitung zulässig. Als Begründung nennt der Hersteller die außergewöhnlichen Anforderungen im Hinblick auf die Hitzebeständigkeit beim Betrieb in hochverdichteten Systemen unter der Last anspruchsvoller KI-Workloads.

Treiber sind der begrenzende Faktor

Für die existierenden Datacenter-Nutzer dieser GPUs haben sich damit die Updates der Treiber de facto erledigt. Ohne die proprietären Treiber von Nvidia, die via Bugfixes stets aktualisiert werden, kann die Hardware nur einen Bruchteil ihrer theoretischen Leistung aufbringen. Beim Bruch der EULAs durch den Nutzer entfällt im Übrigen automatisch die Garantie für die zugehörige Hardware.

Die neuen Nvidia-EULAs haben somit noch weitere Implikationen für Rechenzentren. Anbieter von KI-Systemen müssen auf über 10x teurere GPUs der Tesla-Reihe wie die Tesla „V100“-Chips zurückgreifen (die leistungsschwächere „Quadro“-Familie ist für visuelle Workloads wie industrielles Design optimiert, nicht für neuronale Netze).

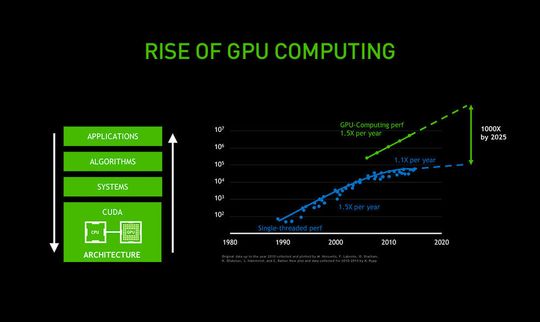

Aufgrund von physikalischen Beschränkungen des Mooreschen Gesetzes klafft die Schere zwischen der Performance einer GPU und einer CPU immer stärker auseinander. Hält dieser Trend an, dürfte die GPU die Single-Threaded-Performance einer CPU bis zum Jahre 2025 um 1.000 Mal übertroffen haben, freut sich Nvidia auf dem hauseigenen Blog.

Doch auch ein Marktführer wäre gut beraten, den Tag nicht vor dem Abend zu loben.

Die IPUs, DPUs, DLUs...

GPUs stellen bei Weitem nicht die einzige Möglichkeit dar, den Leistungshunger von AI-Anwendungen zu sättigen. Darauf wetten sowohl risikoscheue Chip-Riesen wie Intel und Fujitsu als auch die VC-Investoren hinter einer ganzen Reihe noch größtenteils unbekannter Startups.

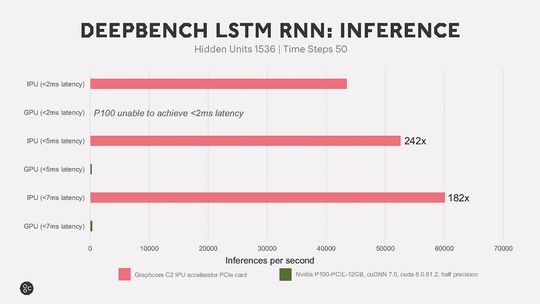

Die britisch-kalifornische Graphcore (https://www.graphcore.ai/) möchte mit der „IPU“ — der Intelligence Processing Unit — die erste von Grund auf für Workloads des maschinellen Lernens optimierte Chip-Architektur entwickelt haben. Die innovative Recheneinheit und das zugehörige Graph Programming-Framework „Poplar“ haben dem Startup unter die Unterstützung von VC-Firmen wie Sequoia und der Robert Bosch Venture Capital GmbH beschert.

Das kalifornische Startup Wave Computing ist mit der „Wave DPU“ (Dataflow Processing Unit) im Rennen. Das Unternehmen hat eine Technologie entwickelt, welche die Engpässe konventioneller Systemarchitekturen durch den Verzicht auf das CPU/GPU-Co-Prozessor-Schema zu beheben versucht. Mit einer hoch skalierbaren 3U-Appliance für maschinelles Lernen im Datencenter möchte Wave Computing die Fähigkeiten der neuen Architektur unter Beweis stellen.

Die kalifornische Cerebras Systems entwickelt Chips für neuronale Netze, bisher noch im Stealth-Modus.

Fujitsu hat mit der „DLU“ (Deep Learning Unit) einen eigenen Weg eingeschlagen. Seine beeindruckenden Leistungsmerkmale verdankt die DLU unter anderem einem neuen Datentyp namens „Deep-Learning-Integer“ und dem „INT8“,16-Akkumulierer der DPU. Sie verleihen dem Prozessor die Fähigkeit, Ganzzahlberechnungen im Inneren tiefer neuronaler Netze mit variabler Präzision von 8 Bit, 16 Bit und 32 Bit durchzuführen, ohne dabei die Genauigkeit des Gesamtmodells aufs Spiel zu setzen.

:quality(80)/images.vogel.de/vogelonline/bdb/1332200/1332226/original.jpg)

Fast so schnell wie ein Quantenrechner

Fujitsu bringt den Akzelerator-Chip Digital Annealer 2018 heraus

Eine von Grund auf neu entwickelte ISA (Instruction Set Architecture) ermöglicht die Durchführung von Berechnungen mit einer variablen Präzision dank der Unterstützung des so genannten Deep-Learning-Integers (siehe: „Spezialisten und Generalisten: Deep-Learning mit Fujitsus DLU und Post-K“).

Intel outside? Mehrfach abgesichert

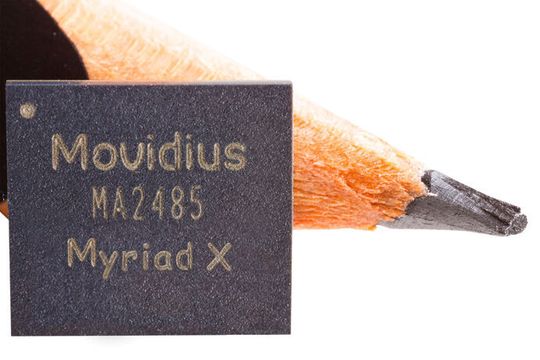

Auch Intel hat die Menetekel der Zeit bereits erkannt. Nach Ablauf des Lizenzabkommens mit Nvidia hat sich der CPU-Riese mit GPU-Technologie von AMD versorgen lassen, vorerst allerdings nur bei Notebooks. Bei KI-Anwendungen möchte Intel offenbar nichts dem Zufall überlassen und hat mehrere Pferde im Rennen: FPGAs von Altera, ASICs von Nervana Systems, einen 49 Quabits starken Quantencomputer namens „Tangle Lake“, neuromorphische Chips „Loihi“ und die „Movidius VPU“ (Vision Processing Unit) für Edge-Anwendungen des Deep Learning in autonomen IoT-Endgeräten.

:quality(80)/images.vogel.de/vogelonline/bdb/1307500/1307572/original.jpg)

Intel Nervana: Erster dedizierter Prozessor für neuronale Netze

Mit Nervana Systems hat Intel für schätzungsweise 408 Millionen Dollar einen SaaS-Plattformanbieter mit einer KI-Cloud erworben. Diese läuft derzeit… auf Nividia Titan X-GPUs. Nervana Engine, ein anwendungsgerecht maßgeschneiderter ASIC-Chip in Entwicklung, soll diese Abhängigkeit demnächst beenden. Der ASIC soll zudem zirka 10x besser abschneiden als die Nividia Maxwell-GPU.

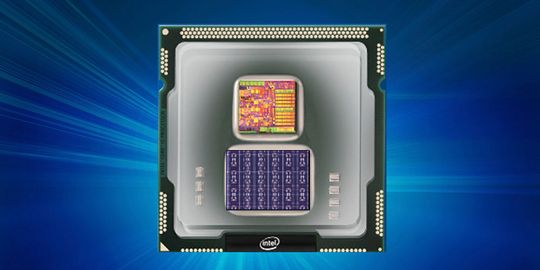

Intel experimentiert auch mit neuromorphischen Chips unter dem Codenamen Loihi. Gefertigt in 14-Nanometer-Technologie verfügt das Technikwunder über insgesamt 130.000 Neuronen und 130 Millionen Synapsen, die als Schaltkreise implementiert wurden.

Doch auch Nvidia möchte nicht alles auf eine Karte setzen. Die „DrivePX“-Plattform der nächsten Generation für autonome Fahrzeuge soll eine hybride Architektur besitzen. Neben einer ARM CPU und einer Volta-GPU kommt eine DLA (Deep Learning Accelerator) in ASIC-Architektur zum Einsatz.

Analysten von Research and Markets bescheinigen dem KI-Markt ein jährliches Wachstum von 57,2 Prozent CAGR. In diesem Tempo dürfte das Marktvolumen bis 2025 auf 58,97 Milliarden Dollar heranwachsen — da gibt es sicherlich hinreichend Platz für mehrere alternative Architekturen.

*Das Autoren-Duo Filipe Pereira Martins und Anna Kobylinska arbeitet für die Soft1T S.a r.l. Beratungsgesellschaft mbH, McKinley Denali Inc. (USA).

(ID:45161858)

:quality(80)/p7i.vogel.de/wcms/2c/6c/2c6ceaad30aeee8c46974275a39c1717/0131220620v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/b7/51/b7517d2828afce2eed6c60c8f4b15e08/0131193094v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/a0/74/a074b1b682c5af4985ac6db2f521efcd/0131131347v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/a5/db/a5db7775305378d9d405e13e60f5e2f8/0130996707v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/d6/efd67bbf37bf217b7fb376c5b6cea3f2/0131214575v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/9d/3d/9d3db3d58b3a3b6b1a07a4b5eae428d5/0131238283v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/b0/20/b020a96ad0479586bce92b4e0be8c5b1/0131172866v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/6e/05/6e0551963ade522e815e481b0866df59/0131270766v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fc/91/fc91634cab380f053be693356d88ab11/0131193486v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/89/97/899791db276100161ea76f79dd649245/0131131469v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/03/53/03531922dce111ec6fa5b65684d9ea1c/0131055174v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/dd/44/dd444ffd9fdf1be2fb62dcc9e40e085f/0131240534v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f4/5b/f45bcf8db2cc67b07fd0378cc3300f4f/0130884384v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/ff/42ff4fc17a11a3fa7065cefc168ef25d/0130824377v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/63/c4/63c4700dcf2d980c5a5c4ed41890c62b/0130812458v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/a7/78/a778073f09b71e34b258aadcc396f100/0130856536v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ad/e9/ade9d0a11085d64eaaacbe51d683beca/0130726498v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/b3/e7b349f9bb427752fd3f4ae4c52c957d/0130852653v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/81/b3/81b359118a0e0e395cdebbddcfa03243/0130668020v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/16/b7/16b7b2637f84403b141e992af44500d9/0131265177v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/b8/26/b82629c5b95d15047e5489328a63a6e0/0131192769v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/17/94/179447f80cab81cfdbadd85c46cc9b72/0131191448v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/e4/d9e4f7b94025360fa28245bfccc07ada/0130927746v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ae/f9/aef9cef6337f8d1593202170a319e812/0130764658v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/49/7a/497af014bb9c80eb964cbd4b170f1af6/0130709118v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/8a/ba/8abadeb121d645fdb8fb5a68d6a4c9b8/0130541481v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8b/64/8b64e9369f05a2b07bfa2c76e53819be/0131210510v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/0c/ec/0cecbad201eb5d74f1ea8f9ec3a4f7a0/0128040845v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/8e/1f/8e1f9fa0a40402c37826489eb3bff4a6/0131226935v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/04/58/0458d319fcf6c748ac43aef05ffee535/0131244622v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f3/da/f3dacd38e5834ae3f3c9d0a4bc9664d3/0113348475.jpeg)

:quality(80)/p7i.vogel.de/wcms/90/f5/90f56ec6cb3ddbdabca2162fd5477836/0113078524.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/09/0f097990002b7600075e43c92af4a3fd/0110524571.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/ae/66ae9e32738784b57e2ad8c1a4b0986f/0109756744.jpeg)

:quality(80)/p7i.vogel.de/wcms/41/ec/41ecbc8077275d54daf5895ae6f98b6c/0130998245v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/00/24/0024808d38d25431ae2719d3f8252908/0130726727v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ee/3f/ee3f063b82737f0369c09ba7854587b5/0127234708v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f1/f0/f1f007a4518fa65d3cb0ea5ca465142a/0121300054v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/a8/28/a828f76369267628d833a12c26dd6579/0121131534v3.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/64/e4/64e4be0db6ddc/rittal-4c-w.png)

:fill(fff,0)/p7i.vogel.de/companies/60/de/60ded37a20a00/logo-vertiv.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/66/c3/66c33d1f71ef2/daxten-logo-600-x-600.jpeg)

:quality(80)/p7i.vogel.de/wcms/69/1b/691ba32faec8b67acb3eb374e957e855/0127069692v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/45/3c/453c4ba732be7aaf230a409dcffbd626/0126690861v1.jpeg)