Rechnerplattformen für Künstliche Intelligenz Spezialisten und Generalisten: Deep-Learning mit Fujitsus DLU und Post-K

Der KI-Veteran und Deep Learning-Vorreiter Fujitsu möchte mit einer neuartigen Prozessorarchitektur, der „DLU“, die Pro-Watt-Leistung tiefer neuronaler Netze auf einmal verzehnfachen. Ein Nachfolger des „K“-Computers, getauft auf die Bezeichnung „Post-K“, soll zugleich das wahre Leistungspotenzial von „Fujitsu Tofu Interconnect“ in einer erweiterten Ausführung unter Beweis stellen.

Anbieter zum Thema

Zwischen den Anforderungen von Deep-Learning-Workloads und der Performance marktüblicher Hardware klafft die Schere weiter auf. Quantencomputer, zweifelsohne einer der Hoffnungsträger vieler rechenintensiver Anwendungen, können aufgrund ihrer (zu) engen Spezialisierung gerade diese Lücke nicht schließen.

Denn weder rückgekoppelte neuronale Netze, die für die Verarbeitung von Ein- und Ausgabe variabler Länge in Anwendungen bevorzugt werden, welche menschliches Denken simulieren sollen, noch CNNs/ConvNets - zur Verarbeitung der Ein- und Ausgabe fester Länge in Anwendungen wie dem maschinellen Sehen oder der Erkennung von Bildmotiven - lassen sich mit Quantenchips sinnvoll umsetzen. Doch gerade künstliche neuronale Netze stellen das Rückgrat des Tiefen Lernens dar.

Deep-Learning-Workloads werfen auch für konventionelle Chips nicht zu unterschätzende Herausforderungen auf, und zwar sowohl im Hinblick auf den Leistungsverbrauch als auch auf die dringend benötigten Fähigkeiten zur massiven Parallelisierbarkeit. Beide Ziele stehen in einem klaren Widerspruch zueinander.

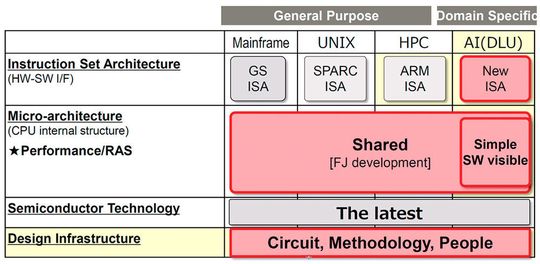

Fujitsu möchte den verschiedenen Herausforderungen der bevorstehenden IT-Ära des „tiefen Lernens“ mit einer neuartigen KI-optimierten Chiparchitektur namens DLP (Deep Learning Unit) begegnen (siehe auch: „Robust und schnell - die neuen Primergy- und Primequest-Modelle, Die Fujitsu-Offensive mit dem Prozessor Intel Xeon Scalable“).

Das „Kerngeschäft“: eine Hochleistungsarchitektur für massive Parallelisierbarkeit

Eine DLU, die Deep Learning Unit, basiert auf einer Vielzahl heterogener, Domain-spezifischer Verarbeitungseinheiten, den so genannten DPUs (Deep Learning Processing Units), die von einem oder mehreren „Master“-Prozessorkernen kontrolliert und orchestriert werden.

Jede DPU verfügt über 16 “Deep Learning Processing Elements”, DPEs. In einer DLU mit sechs DPUs kommen so 96 DPEs zusammen. Jede DPE beinhaltet wiederum acht SIMD-Ausführungseinheiten (Single Instruction/Multiple Data); in dieser Architektur erfolgt die parallele Verarbeitung eines Befehls gleichzeitig über mehrere Datensätze hinweg.

Die DPEs sind untereinander mit einem „On-Chip“-Hochgeschwindigkeitsnetzwerk verbunden. Ein großzügiger, vollständig in Software kontrollierbarer Registerspeicher und die hohe Breite der SIMD-Ausführungseinheiten sollen die hohe Leistung der Hardware voll ausreizen können.

Jedes DLU-Prozessorpaket ist nach außen hin mit einer HBM2-Schnittstelle für 3D-gestapelten DRAM ausgestattet. 3D-gestapelter Arbeitsspeicher gilt allgemein als eine Voraussetzung für Exascale-Systeme der (nahen) Zukunft. Fujitsu hat offenbar Großes im Sinne.

Die hohe Anzahl von Prozessorkernen und die leistungsstarke On-chip-Konnektivität fördern massive Parallelisierbarkeit zu Tage. Eine von Grund auf neu entwickelte ISA (Instruction Set Architecture) ermöglicht die Durchführung von Berechnungen mit einer optimierten — nämlich variablen — Präzision dank der Unterstützung des sogenannten Deep-Learning-Integers.

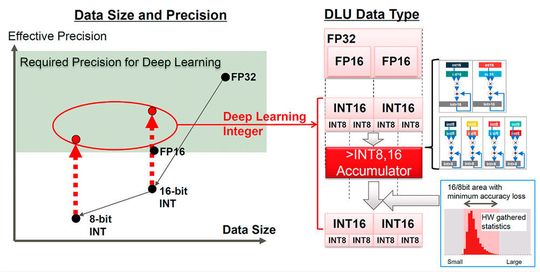

Deep-Learning-Integer: optimal „auf den Punkt gebracht“

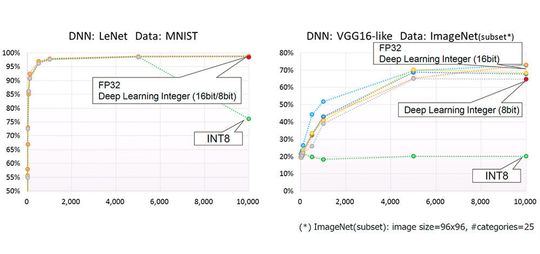

Seine beeindruckenden Leistungsmerkmale verdankt die DLU unter anderem einem neuen Datentyp namens „Deep-Learning-Integer“ und dem „INT8“,16-Akkumulierer der DPU. Sie verleihen dem Prozessor die Fähigkeit, Ganzzahlberechnungen im Inneren tiefer neuronaler Netze mit variabler Präzision von 8 Bit, 16 Bit und 32 Bit durchzuführen, ohne dabei die Genauigkeit des Gesamtmodells aufs Spiel zu setzen.

Das Ausführen von Deep-Learning-Workloads läuft bisher auf das Lösen neuronaler Netzwerkgleichungen hinaus. Anstatt jede Gleichung im Rahmen eines neuronalen Netzwerks mit einer festen Genauigkeit zu lösen, zum Beispiel als FP32, also als eine Fließkommaberechnung in 32 Bit, kann die Fujitsu-DLU mit gemischter Eingabegenauigkeit wahlweise in 8 Bit, 16 Bit und 32 Bit arbeiten und die Resultate dennoch als 32-bittigen Fließkommawert ausgeben.

Der innovativer Ansatz geht aus der Erkenntnis hervor, dass sich umfangreiche tiefe neuronale Netze mit punktuell reduzierter numerischer Präzision nahezu ohne Verlust trainieren lassen. Bei Ganzzahlberechnungen mit einer Präzision von lediglich 8 und 16-Bit soll eine effektive Genauigkeit von 32 Bit erreicht werden können, sofern das verwendete Modell hinreichend umfassend und komplex angelegt ist. Diese Optimierung resultiert dann in einem Performance-Gewinn bei gleichzeitiger Senkung des Energieverbrauchs gegenüber FP32 (Gleitkommaberechnungen in 32 Bit).

So erreicht Fujitsu zwei gegensätzliche Ziele auf einen Schlag, betonte Takumi Maruyama, stellvertretender Vizepräsident von Fujitsu für den Geschäftsbereich AI Platform/Advanced System Research & Development Unit, in seinem viel beachteten Auftritt auf der diesjährigen ISC High Performance-Messe 2017 in Frankfurt.

Moderne SIMD-Befehlssätze sind oft auf Gleitkommazahlen hin ausgerichtet. Bei den neuesten GPUs könnte die Reduktion der numerischen Präzision tiefer neuronaler Netze auf 8 Bit bei Ganzzahlberechnungen keinen derart massiven Leistungsvorteil bringen. Fujitsu könnte mit diesem Ansatz tatsächlich einen erheblichen Vorteil herausarbeiten.

Tofu2 Interconnect

Ein weiteres Highlight der DLU bildet das 6-dimensionale Tofu2-Interconnect, eine Technologie von Fujitsu, die hier in einer „On-die“-Ausführung zum Zuge kommt. Tofu2-Interconnect hat sich bereits in Fujitsus Supercomputern der „Prime-HPC“-Familie bewährt. „Fujitsu Prime HPC FX100“ skaliert beispielsweise auf bis zu hunderttausend Knoten für bis zu 100 Petaflops Leistung.

Tofu Interconnect wurde ursprünglich für den K-Supercomputer entwickelt und hat sich seither in Benchmarks wie dem HPCG (High Performance Conjugate Gradient) bewährt. Der K Computer hat kürzlich beim HPCG-Benchmark zum zweiten Mal in Folge den ersten Platz belegen können.

Ein Blick auf die Top 10 der Top-500-Supercomputerliste zeigt ganz deutlich, dass von einem großen Wurf zum nächsten jeweils sehr viel harte Arbeit dazwischenliegt. Fujitsu belegt hier unter den ersten zehn Supercomputern der Weltspitze derzeit gleich zwei begehrte Positionen: die Nummer 7 mit dem Oakforest-PACS (beim Joint Center for Advanced High Performance Computing in Japan) und die Nummer 8 (mit dem K Computer bei Riken).

Wichtiger als Linpack ist HPCG

Beim Oakforest-PACS handelt es sich um eine „Primergy CX1640 M1“ mit dem „Intel Xeon-Phi“-Beschleuniger, die es mit ihren 556.104 Kernen auf eine Spitzenperformance in Höhe von 13.554,60 TFlops/Sek. (Rmax) und eine theoretische Maximalleistung (Rpeak) von 24.913,50 TFlops/Sek. bringt.

K Computer basiert auf „Sparc-64-VIIIfx“-Technologie mit Tofu-Interconnect. Im Innern werkeln hier 705.024 Kerne mit 10.510,00 TFlops pro Sekunde Spitzenperformance (Rmax) und einer theoretischen Maximalleistung (Rpeak) von 11.280,40 TFlops pro Sekunde.

Der Top-500-Liste liegt der Linpack-Benchmark zugrunde. Die hier eingesetzten Bibliotheken sind allerdings ausschließlich darauf ausgelegt, die Fließkommafähigkeiten eines Systems zu messen. Um die Leistung neuartiger Systemarchitekturen adäquat zu bewerten, sind möglicherweise neuere Benchmarks wie der HPCG erforderlich.

Der K - und jetzt der Post-K

IM HPCG-Benchmark konnte der K Computer mit seinen 82.944 Rechenknoten auch diejenigen sieben Supercomputer schlagen, die in der Top-500-Liste eigentlich einen höheren Rang einnehmen. Anders als der Linpack beschränkt sich der HPCG-Benchmark nicht auf die Geschwindigkeit der Fließkommaoperationen.

Denn ein gutes Ergebnis beim HPCG-Benchmark erfordert „eine starke und vielseitige Speichersystemleistung, eine hervorragende Performance des Interconnect-Netzwerks im Ausbau (at scale) und eine insgesamt ausgewogene Systemarchitektur“, kommentierte der leitende Entwickler des Benchmarks, Mike Heroux von Sandia National Laboratories. Die Preisverleihung fand im Übrigen auf der ISC High Performance in Frankfurt statt.

In Zusammenarbeit mit Riken, Japans größter umfassender Forschungseinrichtung (Advanced Institute for Computational Science, AICS), wo der K Computer seinen Dienst verrichtet, entwickelt Fujitsu seinen Nachfolger, treffend auf den Namen Post-K getauft. Fujitsu verzichtet hier auf den „Sparc V9-ISA“ (Instruction Set Architecture) zugunsten des Befehlssatzes „ARM v8-A“. Das System trumpft mit einer SIMD-Bandbreite von 512 Bit (ein erheblicher Sprung von den 128 Bit des K-Computers) und wird mit einer Enhanced-Edition von Tofu Interconnect ausgestattet.

Bei dem Post-K handelt es sich um einen Allzweck-Supercomputer, der unter anderem auch Deep-Learning-Workloads meistern können soll. Im Hinblick auf eben diese Aufgabenstellung bietet das System Unterstützung für Gleitkommazahlenberechnungen mit punktuell optimierter Präzision, also in 64 Bit, 32 Bit oder 16 Bit (FP16) in Abhängigkeit von den Leistungsanforderungen der betreffenden Anwendung (von linearer Algebra über Molekulardynamik bis hin zum Tiefen Lernen).

Die Bewertung der Autoren

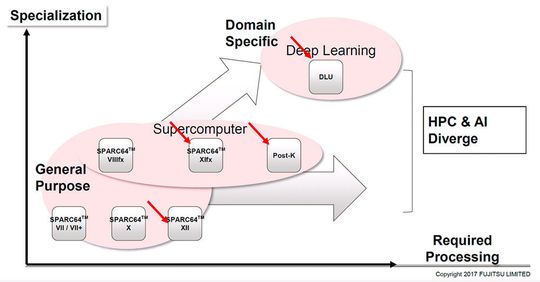

Fujitsus Antwort auf die physikalischen Grenzen des Mooreschen Gesetzes in seiner klassischen Form beruht auf der massiven Parallelisierbarkeit Workload-gerechter Spezialprozessoren. Um den Anforderungen aktueller und künftiger KI-Anwendungen besser gerecht zu werden, müssen HPC- und KI-Architekturen demnach divergieren.

Dieser Grundsatz reflektiert sich bereits in der aktuellen Roadmap von Fujitsu. Allzweck-Supercomputer bekommen in dem Post-K-System einen würdigen Nachfolger. Mit einer Vielzahl ausgefallener technischer Kniffe der massiv skalierbaren DLU-Architektur möchte Fujitsu die Ausführung spezialisierter KI-Workloads mit einem um bis zu 90 Prozent reduzierten Energieverbrauch ermöglichen. Bei gleichbleibender Wattzahl wird so im Vergleich zu alternativen Lösungen die 10-fache Performance erzielt.

Dank massiver Parallelisierbarkeit dürfte Fujitsu dem Phänomenon des Mooreschen Gesetzes — passend zum Anbruch der KI-Revolution — im Bereich des Tiefen Lernens eine Menge neuer Dynamik verleihen.

Das Autoren-Duo

Filipe Pereira Martins und Anna Kobylinska arbeiten für die Soft1T S.a r.l. Beratungsgesellschaft mbH, McKinley Denali Inc.(USA).

(ID:44817146)

:quality(80)/p7i.vogel.de/wcms/2c/6c/2c6ceaad30aeee8c46974275a39c1717/0131220620v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/b7/51/b7517d2828afce2eed6c60c8f4b15e08/0131193094v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/a0/74/a074b1b682c5af4985ac6db2f521efcd/0131131347v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/a5/db/a5db7775305378d9d405e13e60f5e2f8/0130996707v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/d6/efd67bbf37bf217b7fb376c5b6cea3f2/0131214575v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/9d/3d/9d3db3d58b3a3b6b1a07a4b5eae428d5/0131238283v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/b0/20/b020a96ad0479586bce92b4e0be8c5b1/0131172866v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/6e/05/6e0551963ade522e815e481b0866df59/0131270766v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fc/91/fc91634cab380f053be693356d88ab11/0131193486v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/89/97/899791db276100161ea76f79dd649245/0131131469v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/03/53/03531922dce111ec6fa5b65684d9ea1c/0131055174v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/dd/44/dd444ffd9fdf1be2fb62dcc9e40e085f/0131240534v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f4/5b/f45bcf8db2cc67b07fd0378cc3300f4f/0130884384v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/ff/42ff4fc17a11a3fa7065cefc168ef25d/0130824377v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/63/c4/63c4700dcf2d980c5a5c4ed41890c62b/0130812458v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/a7/78/a778073f09b71e34b258aadcc396f100/0130856536v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ad/e9/ade9d0a11085d64eaaacbe51d683beca/0130726498v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/b3/e7b349f9bb427752fd3f4ae4c52c957d/0130852653v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/81/b3/81b359118a0e0e395cdebbddcfa03243/0130668020v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/16/b7/16b7b2637f84403b141e992af44500d9/0131265177v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/b8/26/b82629c5b95d15047e5489328a63a6e0/0131192769v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/17/94/179447f80cab81cfdbadd85c46cc9b72/0131191448v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/e4/d9e4f7b94025360fa28245bfccc07ada/0130927746v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ae/f9/aef9cef6337f8d1593202170a319e812/0130764658v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/49/7a/497af014bb9c80eb964cbd4b170f1af6/0130709118v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/8a/ba/8abadeb121d645fdb8fb5a68d6a4c9b8/0130541481v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8b/64/8b64e9369f05a2b07bfa2c76e53819be/0131210510v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/0c/ec/0cecbad201eb5d74f1ea8f9ec3a4f7a0/0128040845v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/8e/1f/8e1f9fa0a40402c37826489eb3bff4a6/0131226935v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/04/58/0458d319fcf6c748ac43aef05ffee535/0131244622v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f3/da/f3dacd38e5834ae3f3c9d0a4bc9664d3/0113348475.jpeg)

:quality(80)/p7i.vogel.de/wcms/90/f5/90f56ec6cb3ddbdabca2162fd5477836/0113078524.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/09/0f097990002b7600075e43c92af4a3fd/0110524571.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/ae/66ae9e32738784b57e2ad8c1a4b0986f/0109756744.jpeg)

:quality(80)/p7i.vogel.de/wcms/41/ec/41ecbc8077275d54daf5895ae6f98b6c/0130998245v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/00/24/0024808d38d25431ae2719d3f8252908/0130726727v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ee/3f/ee3f063b82737f0369c09ba7854587b5/0127234708v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f1/f0/f1f007a4518fa65d3cb0ea5ca465142a/0121300054v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/a8/28/a828f76369267628d833a12c26dd6579/0121131534v3.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/68/2d/682dd583dcc4c/fsas-afc-horizontal-2-positive-rgb-nov24.png)

:fill(fff,0)/p7i.vogel.de/companies/63/e5/63e5f25ac31ef/logo.png)

:quality(80)/p7i.vogel.de/wcms/4e/72/4e722e75ef31bebe567b43bb0401dce2/0127017259v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/95/d9955bf978b6116770a77ae363ebcdde/0129793217v2.jpeg)