Softwaredefiniertes Speichergewebe Was ist Gen-Z?

Mit „Gen-Z“ entsteht ein offener Standard für ein systemweites Interconnect für speichersemantischen Zugriff auf Speicherkomponenten und Geräte über eine Direktanbindung, dedizierte Switches oder Netzwerkgewebe. Das Projekt Gen-Z hat zum Ziel, ein dringend benötigtes Gleichgewicht zwischen der Leistung von Compute und der Performance von Arbeitsspeicher herzustellen.

Anbieter zum Thema

Das Gen-Z Interconnect trägt der Tatsache Rechnung, dass das Aufkommen von Hardwarebeschleunigern wie GPUs und FPGAs ganz neue Anforderungen an den Arbeitsspeicher stellt während die explodierende Datenflut der KI-Ära althergebrachte Systemarchitekturen in die Knie zwingt. Das führt bei speicherlastigen Workloads zwangsweise zur Überprovisionierung von Compute.

Flaschenhals Arbeitsspeicher

Für ein Unternehmen hängt der Wert seiner Daten davon ab, wie zeitnah sich daraus konkrete Erkenntnisse ableiten lassen. Zwischen dem explodierenden Datenvolumen und dem nachlassenden Wachstum der Compute-Leistung klafft jedoch seit Jahren eine Schere auf. Die Bedeutung der Datenanalyse in Echtzeit nimmt zu während sich die hierzu erforderliche Rechenleistung immer eindeutiger zum relevanten Flaschenhals mausert.

Der Technologie-Unterbau heutiger IT-Systeme sei das Resultat von „60 Jahren an Kompromissen“, glauben HPE-Forscher wie Dr. Kim Keeton, Distinguished Technologist bei Hewlett Packard Enterprise. Auch so Standards wie DDR-Speicher und PCI sollen ausgedient haben.

In heutigen Computersystemen sind der Arbeitsspeicher und die Storage voneinander getrennt. 90 Prozent der Ressourcen eines Computersystems gingen „einfach nur darauf, Daten zwischen dem Arbeitsspeicher und dem permanenten Speicher hin und her zu schaufeln“, sagte HPE-Chef Antonio Neri in einer Keynote. Diese Verschwendung müsse endlich ein Ende finden.

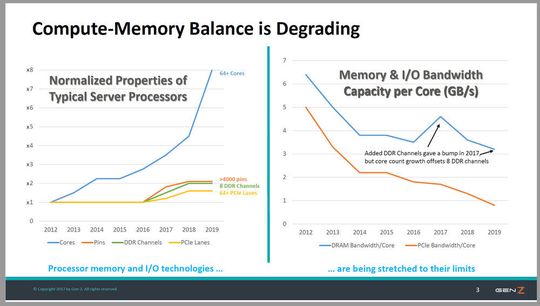

Das Aus für Prozessor-zentrisches Computing

Während sich die Speicherkapazität pro CPU-Kern seit Jahren kaum geändert hat, nimmt die Bandbreite des Arbeitsspeichers pro CPU-Kern von Generation zu Generation sogar noch ab. „Wir sind an einem Punkt angelangt, an dem wir zwar Compute-Einheiten zu einem System hinzufügen, aber sie unmöglich mit Daten beliefern können“, “, sagt Michael Krause, VP und Fellow Engineer bei HPE und einer der Mitgründer des Gen-Z Konsortiums. „Wir möchten stattdessen in der Lage sein, eine sehr hohe Bandbreite bereitzustellen und eine sehr geringe Latenz zu gewährleisten und ein Gleichgewicht in unseren Computersystemen wiederherzustellen“.

Prozessor-zentrisches Computing müsse unbedingt einer von Grund auf neu konzipierten Systemarchitektur weichen. Ansätze wie „speichergetriebenes“ Computing von HPE und Experimentalarchitekturen wie „The Machine“ (siehe hierzu auch: „Flache Storage-Hierarchien und Memory-Pools treffen auf Gen-Z-Connectivity – Paradigmenwechsel angesagt: Memory-driven und/ oder In-Network-Computing“ sollen Abhilfe schaffen, doch sie benötigen neue Interconnects.

Bestehende Systemarchitekturen bieten keinerlei Möglichkeit, die verfügbaren Ressourcen bis in die Ebene der Speichersemantik zu disaggregieren. Jeder Versuch, eine solche Technologie zu implementieren, würde sich sofort auf die Bandbreite und Latenz der betreffenden Komponenten auswirken und die Vorteile zusammensetzbarer Infrastruktur schnell wieder zunichtemachen. Es wird eine völlig neue, Speicher-zentrische Architektur benötigt. Eine neue Systemarchitektur ist längst überfällig.

Native Semantik des Speichers

Gen-Z verwendet auf der physischen Ebene eine serielle Schnittstelle mit elektrischer (Kupfer) oder optischer (Glasfaser) Konnektivität, wahlweise symmetrisch oder asymmetrisch.

Die Semantik des Byte- und diejenige des blockadressierbaren Speichers unterscheiden sich wie Tag und Nacht voneinander. In der Vergangenheit war der Arbeitsspeicher, zum Beispiel DRAM, durch Volatilität gekennzeichnet während Storage-Medien, beispielsweise HDDs oder SDDs, durch Datenpersistenz trumpften. Das Aufkommen von SCM (Storage Class Memory) hat diese Trennung aufgehoben: SCM beherrscht die Semantik des Byte-adressierbaren Speichers, ohne jedoch auf die Datenpersistenz zu verzichten.

Mit dem Gen-Z-Interconnect soll jedes Gerät mit jedem anderen Gerät unter Verwendung derselben Anweisungen – also mit Hilfe derselben Semantik – kommunizieren können als ob es sich dabei um den eigenen lokalen Arbeitsspeicher des Systems handelte. Gen-Z bietet hierzu ein offenes und zudem auch noch lizenzfreies speichersemantisches Protokoll, welches nicht mehr dem Speicher-Controller der CPU unterliegt.

Verkürzte Latenzen

Durch den reduzierten Overhead sinkt auch die Latenz der Zugriffe. Im Hinblick auf den Datendurchsatz ist von mehr als 100 Gigabit pro Sekunde (GBp/s) und im Hinblick auf die Latenz von weniger als 100 Nanosekunden (ns) die Rede.

So lässt sich beispielsweise ein via Gen-Z angeschlossener Speicher in einer Prozessorspeicherverwaltungseinheit (MMU) abbilden. Jede Lade-, Speicher- oder Atomic-Operation eines Prozessors wird so transparent in eine Gen-Z-Lese-, Schreib- oder Atomic-Operation übersetzt und zur Zielspeicherkomponente transportiert.

In ähnlicher Weise unterstützt Gen-Z die Operationen „put“ und „get“ des Puffers und kann dadurch bis zu 232 Datenbytes zwischen Puffern verschiedener Komponenten ohne die Beteiligung des Prozessors hin und her schieben. Dies schafft Potenziale zur Vereinfachung von Hardwarearchitekturen im Rechenzentrum.

Gen-Z soll speichersemantische Konnektivität innerhalb eines Compute-Knoten wie auch – via Switches im Gen-Z-Gewebe – zwischen Racks ermöglichen und sowohl im Kern-Datacenter als auch in Edge-Topologien und sogar im High Performance Computing (HPC) eine Rolle spielen. Der Weg über einen Gen-Z-Switch fügt zur Kommunikation jeweils eine Latenz von nur 30 Nanosekunden hinzu.

Gen-Z-Speicherserver könnten zum festen Bestandteil der Rechenzentrumslandschaft werden und datenzentrische Workloads wie Machine Learning (ML) oder Deep learning (DL) um zusätzliche Kapazitäten bedarfsgerecht erweitern.

Neue Interconnects für speicherzentrische Systemarchitekturen der Zukunft

Gen-Z entsteht unter der Schirmherrschaft einer Allianz führender Unternehmen der Computerindustrie, des Gen-Z-Konsortiums. Die Technologie ist offen und frei von Lizenzgebühren. Zu den treibenden Kräften hinter Gen-Z zählen AMD, ARM, Cray, Dell EMC, Google, HPE, Huawei, Lenovo, Microsoft, Samsung Semiconductors, Xilinx und andere. Intel ist nicht mit von der Partie.

Gen-Z galt seinerzeit als eine Kriegserklärung der IT-Branche gegen Intel und seine proprietären Interconnects. Der Chip-Riese aus dem kalifornischen Mountain View hat einen eigenen Weg eingeschlagen und entwickelt mit einem ebenfalls offenen Standard namens „Compute Express Link“ (CXL) eine Alternative zu Gen-Z mit latenzsensiblen Workloads im Visier. CXL macht konzeptionelle Anleihen am PCI-Stack und ist die kostengünstigere Alternative zu Gen-Z innerhalb eines Knoten. Viele Beobachter sehen CXL als Intels „Auffahrt auf die Gen-Z-Autobahn”. Doch diese Prognose hat sich noch nicht bewahrheitet.

Gen-Z entwickelt sich zum universellen Interconnect und ist Intel ein Dorn im Auge. CXL fokussiert auf die Konnektivität innerhalb eines Knoten und „spricht“ bisher nicht nativ mit Gen-Z. Beide Interconnects könnten dennoch dank Bridges in einem disaggregierten System miteinander koexistieren. Auch „Ultra Path Interconnect“ (UPI) von Intel braucht eine Bridge zu Gen-Z - und ist bereits als Proof-of-Concept verfügbar.

Unter der Bezeichnung „CCIX“ reift auch noch ein anderer Standard für ein Speicher-Interconnect. CCIX steht für Cache Coherent Interconnect for Accelerators und bedeutet so viel wie Cache-kohärenter Interconnect für Beschleuniger. Mit diesem Standard können Prozessoren, die auf unterschiedlichen Befehlssatzarchitekturen basieren, die Vorteile der Cache-kohärenten Datenverarbeitung durch Systemkomponenten in Peer-zu-Peer-Topologien auf eine Reihe von Beschleunigungsgeräten ausweiten, darunter FPGAs, GPUs, Netzwerk-/Speicheradapter, intelligente Netzwerke und benutzerdefinierte ASICs.

Zu den treibenden Kräften dieses Standards zählen AMD, ARM, Fujitsu, Huawei, IBM, Mellanox, Qualcomm und Xilinx. Auch hier ist Intel bisher nicht vertreten.

Eine universelle Speicherschnittstelle?

Gen-Z verspricht Rechenzentren nicht „nur“ einen Leistungssprung mit neuer Hardware, eine verbesserte Energieeffizienz und eine höhere Branchenagilität, sondern nebenbei auch neue Möglichkeiten der Leistungsoptimierung der bereits bestehenden Infrastruktur-Altlasten.

Gen-Z-Hardwarekomponenten lassen sich in die bestehende Unternehmens-IT vollständig transparent einfügen; es sind hierzu weder Änderungen am Betriebssystem noch an der Middleware erforderlich. Der Standard nutzt allerdings neuartige modulare Stecker; zum Teil sollen sie mit bestehenden Anschlüssen und bestehender Verkabelung nutzbar sein. Das Interconnect soll vorerst zwischen verschiedenen Serverknoten vermitteln und auf einen Rack skalieren können.

Die ersten Systeme sind bereits im Kommen.

*Das Autorenduo Anna Kobylinska und Filipe Pereira Martins arbeitet für McKinley Denali Inc. (USA).

(ID:46311433)

:quality(80)/p7i.vogel.de/wcms/2c/6c/2c6ceaad30aeee8c46974275a39c1717/0131220620v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/b7/51/b7517d2828afce2eed6c60c8f4b15e08/0131193094v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/a0/74/a074b1b682c5af4985ac6db2f521efcd/0131131347v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/a5/db/a5db7775305378d9d405e13e60f5e2f8/0130996707v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/d6/efd67bbf37bf217b7fb376c5b6cea3f2/0131214575v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/9d/3d/9d3db3d58b3a3b6b1a07a4b5eae428d5/0131238283v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/b0/20/b020a96ad0479586bce92b4e0be8c5b1/0131172866v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/6e/05/6e0551963ade522e815e481b0866df59/0131270766v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fc/91/fc91634cab380f053be693356d88ab11/0131193486v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/89/97/899791db276100161ea76f79dd649245/0131131469v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/03/53/03531922dce111ec6fa5b65684d9ea1c/0131055174v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/dd/44/dd444ffd9fdf1be2fb62dcc9e40e085f/0131240534v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f4/5b/f45bcf8db2cc67b07fd0378cc3300f4f/0130884384v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/ff/42ff4fc17a11a3fa7065cefc168ef25d/0130824377v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/63/c4/63c4700dcf2d980c5a5c4ed41890c62b/0130812458v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/a7/78/a778073f09b71e34b258aadcc396f100/0130856536v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ad/e9/ade9d0a11085d64eaaacbe51d683beca/0130726498v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/b3/e7b349f9bb427752fd3f4ae4c52c957d/0130852653v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/81/b3/81b359118a0e0e395cdebbddcfa03243/0130668020v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/16/b7/16b7b2637f84403b141e992af44500d9/0131265177v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/b8/26/b82629c5b95d15047e5489328a63a6e0/0131192769v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/17/94/179447f80cab81cfdbadd85c46cc9b72/0131191448v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/e4/d9e4f7b94025360fa28245bfccc07ada/0130927746v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ae/f9/aef9cef6337f8d1593202170a319e812/0130764658v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/49/7a/497af014bb9c80eb964cbd4b170f1af6/0130709118v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/8a/ba/8abadeb121d645fdb8fb5a68d6a4c9b8/0130541481v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8b/64/8b64e9369f05a2b07bfa2c76e53819be/0131210510v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/0c/ec/0cecbad201eb5d74f1ea8f9ec3a4f7a0/0128040845v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/8e/1f/8e1f9fa0a40402c37826489eb3bff4a6/0131226935v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/04/58/0458d319fcf6c748ac43aef05ffee535/0131244622v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f3/da/f3dacd38e5834ae3f3c9d0a4bc9664d3/0113348475.jpeg)

:quality(80)/p7i.vogel.de/wcms/90/f5/90f56ec6cb3ddbdabca2162fd5477836/0113078524.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/09/0f097990002b7600075e43c92af4a3fd/0110524571.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/ae/66ae9e32738784b57e2ad8c1a4b0986f/0109756744.jpeg)

:quality(80)/p7i.vogel.de/wcms/41/ec/41ecbc8077275d54daf5895ae6f98b6c/0130998245v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/00/24/0024808d38d25431ae2719d3f8252908/0130726727v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ee/3f/ee3f063b82737f0369c09ba7854587b5/0127234708v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f1/f0/f1f007a4518fa65d3cb0ea5ca465142a/0121300054v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/a8/28/a828f76369267628d833a12c26dd6579/0121131534v3.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/5f/74/5f7479b1443af/panduit-logo2015-bp-below-aligned-tm.jpg)

:fill(fff,0)/p7i.vogel.de/companies/67/92/67921e1a932db/logo-pqplus---rgb.jpeg)

:quality(80)/p7i.vogel.de/wcms/7a/37/7a37285c34944ac586d3be8ac320ceaa/0126243197v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/2a/4d/2a4dc3648b0a80ad69faed0697837351/0125749477v1.jpeg)