Fortschritte im 3D-Design AMD stellt neue Prozessoren für Rechenzentren vor

„Accelerated Computing“ wird als Synonym für KI-, HPC- oder allgemein schnelles Rechnen gebraucht – mit Computern, die neben CPUs auch Akzeleratoren, Beschleuniger wie GPUs, DPUs, FPGAs und IPUs verwenden. Am Montagabend hat die AMD-Chefin Lisa Su auf der Veranstaltung „Accelerated Data Center Premiere“ die jüngsten Erweiterungen der Rechenzentrums-Produktpalette vorgestellt.

Anbieter zum Thema

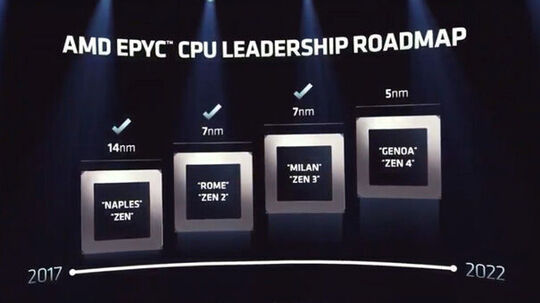

Der „Star“ unter den Produktvorstellungen ist der „weltweit schnellste HPC- und KI-Beschleuniger“, wie Su sagt, „AMD Instinct MI200“ gewesen. Außerdem hat sie einen Ausblick auf die „Epyc“-Prozessoren der 3. Generation mit „AMD 3D V“-Cache gegeben und die Datacenter-Roadmap für den Prozessorkern „Zen 4“, mitsamt Aussicht auf kündigte den neuen „Zen 4c“. Darüber hinaus sind einige der prominenten AMD-Kunden zu Wort gekommen: Ex-Facebook Meta, Microsoft Azure und das Oakridge National Laboratory.

Das US-Forschungsinstitut, das Supercomputer in Exascale-Dimensionen einsetzen will, setzt die Beschleuniger der AM DInstinct-MI200-Serie ein sowie die 3. Generation der Epyc-CPUs für den Supercomputer „Frontier“ ein, der im kommenden Jahr online gehen soll.

Die MI200-Serie basiert auf der „CDNA 2“-Architektur, die in erster Linie für anspruchsvolle wissenschaftliche Berechnungen und maschinelles Lernanwendungen konzipiert ist. Die Produktserie zielt damit auf Anwendungen, die von kompakten Einzelsystemen bis hin zu den größten Supercomputern mit offenen Programmiermodellen reichen. Sie bietet eine Technologie mit bis zu 880 Matrix Cores in der Version „AMD Instinct MI200 OAM“ und bietet volle Double-Precision-Rate und FP64-Matrix-Operationen für HPC-Workloads.

Die integrierte „Infinity Fabric“-Schnittstelle bezeichnet Su als eine der wichtigsten Innovationen in der CDNA-2“-Familie. Sie verbindet zwei Graphics Compute Die (GCD) innerhalb der AMD-GPUs „MI250“ oder „MI250X“ und liefert eine theoretische maximale bidirektionale Bandbreite von bis zu 400 GB/s zwischen den GCDs.

Die CDNA-2-Speichercontroller sind so skaliert, dass sie auf bis zu 128 Gigabyte HBM2e Speicherkapazität zugreifen und eine Bandbreite von 3,2 TB/s nutzen können. Außerdem hat AMD an der Kohärenz geschraubt, was die Zusammenarbeit mit dem Epyc-Prozessor der 3. Generation betrifft (siehe: Video). Neu erfunden ist die 3-D-Gehäusetechnologie, die die Architektur „zu den ersten Multi-Die-GPUs der Branche“ werden lässt.

Die kommenden CPUs

Die kommende Version des Epyc-Prozessors ist „AMD 3D V-Cache“, und sie wird im 1. Quartal 2022 auf den Markt kommen. Die Rechnerhersteller Cisco, Dell Technologies, Lenovo, HPE und Supermicro planen, Server mit diesen Prozessoren anzubieten.

Die Innovation steckt in den Gehäuseinnovationen, die eine kontinuierliche Skalierung der Prozessorleistung ermöglichen, um insbesondere die hohen Rechenanforderungen von HPC-Anwendungen erfüllen zu können, während traditionelle Ansätze zur Erfüllung die Vergrößerung der Chips und/oder die Verkleinerung der Logikschaltungen sind. Doch diese Ansätze haben ihre Grenzen. Das Mooresche Gesetz, das besagt, dass sich die Zahl der Transistoren in einem dichten integrierten Schaltkreis alle zwei Jahre verdoppelt, verlangsamt sich gerade dann, wenn die Nachfrage nach leistungsfähigeren Prozessoren steigt.

AMD antwortet auf diese Herausforderung mit seiner 3D-Chiplet-Technologie. AMD-Chefin Su hat in ihrer Keynote einen Ausblick auf den Einsatz der AMD-Packaging-Technologie im Rechenzentrum gegeben. Die erste CPU hat den Codenamen „Milan-X“ getragen. Nach ihren Angaben bietet das Design im Vergleich zum Vorgänger eine durchschnittliche Leistungssteigerung von 50 Prozent bei ausgesuchten technischen Datenverarbeitungsaufgaben.

Das 3D-Design

Die Idee: Chiplets ersetzen monolithische SoCs (System on a Chip) durch mehrere einfachere Bausteine, die in der Regel günstiger in der Herstellung sind. Diese einfacheren Bausteine können dann gemischt und angepasst werden, um einer eine Vielzahl von Anforderungen. Die zusätzliche Komplexität des Zusammenbaus mehrerer Blöcken zu einem einzigen System wird durch Flexibilität im Design „mehr als ausgeglichen“.

Die Epyc-Prozessoren der 2. Generation, die 2019 eingeführt worden sind, waren die Multi-Chip-Modul-Architektur (MCM). Diese MCM steigert die Leistung, indem sie verschiedene Prozessorknoten für CPU und E/A im selben Gehäuse unterbringt. Die 3. Generation, die Anfang dieses Jahres auf den Markt gekommen ist, nutzt dieselbe Architektur.

Neu ist der „3D V-Cache“. Damit adressiert AMD das Problem, dass sich beim Hinzufügen von Chiplets zu einem größeren SoC mehr Abstand zwischen den Komponenten ergibt, was die Latenzzeit erhöht. 3D V-Cache ist laut AMD die erste x86-CPU-Technologie mit echtem 3D-Die-Stacking. AMD nutzt dafür eine „TSMC 3D Fabric“ Technologie.

Der Meta-Kunde

Epyc-Prozessoren der 3. Generation mit AMD 3D V-Cache bieten die gleichen Fähigkeiten und Funktionen wie die Epix-CPUs ohne und sind durch ein BIOS-Upgrade sofort kompatibel. Das erlaubt eine einfache Einführung und Leistungssteigerung.

AMD gab bekannt, dass Meta das neueste große Hyperscale-Cloud-Unternehmen ist, das AMD EPYC-CPUs einsetzt. AMD und Meta arbeiteten gemeinsam an der Definition eines offenen, Cloud-Scale, Single-Socket-Servers, der auf Leistung und Energie-Effizienz ausgelegt ist und auf dem Epyc-Prozessor der 3. Generation. Weitere Details werden auf dem „Open Compute Global Summit“, der seit gestern läuft, diskutiert.

Zu den jüngsten prominenten Kunden von Epyc-Prozessoren gehören Meta und Microsoft Azure. Nach eigenen Angaben rechnet man bei Meta damit, im Jahr 2022 mehrere Milliarden Dollar für Rechenzentren, Server und Büros auszugeben. Das Unternehmen rechnet im kommenden Jahr mit Investitionsausgaben in Höhe von 29 bis 34 Milliarden Dollar; 19 Milliarden Dollar sind es in diesem Jahr.

Zu den Lieferanten gehört AMD. Gemeinsam arbeite man an der Definition eines offenen, Cloud-basierten Single-Socket-Servers, der auf Leistung und Energie-Effizienz ausgelegt ist. Angetrieben wird er wohl durch einen Epyc-Prozessor der dritten Generation. Weitere Details werden auf dem Open Compute Global Summit Ende dieser Woche diskutiert.

Vorschau live, bald weltweit verfügbar

Bei Microsoft Azure und dem HPC-Angebot per virtueller Maschinen unter Einsatz vom AMD-Technik ist man schon weiter. Dieses steht seit vorgestern mit Epyc 3D V-Cache in der Private Preview zur Verfügung. In den kommenden Wochen werden der Service auf breiter Basis eingeführt, hat die AMD-Präsidentin ankündigen können.

Um genau zu sein handelt es sich um virtuelle „Azure HBv3“-Maschinen. Laut Microsoft verbesserten die jüngsten Prozessoren die Leistung, Skalierungs- und Kosteneffizienz für eine Vielzahl von speicherabhängigen Arbeitslasten wie CFD, explizite Finite-Elemente-Analysen, Geowissenschaften, Wettersimulationen und RTL-Workflows erheblich.

Im Vergleich zur aktuellen HBv3-Serie mit den Epyc-v3-Prozessoren, die bereits die leistungsstärkste VM für HPC-Workloads in der Public Cloud sei, werden die Kunden eine bis zu:

- 80 Prozent höhere Leistung für CFD

- 60 Prozent höhere Leistung für EDA RTL

- 50 Prozent höhere Leistung für explizite FEA

- 19 Prozent höhere Leistung für Wettersimulationen erwarten dürfen, teilt Microsoft mit.

So will der Cloud-Anbieter alle VMs der HBv3-Serie weltweit in Kürze mit Milan-X-Prozessoren aufrüsten. Dieses Upgrade werde ohne zusätzliche Kosten über die bestehenden Preise für VMs der HBv3-Serie hinaus und ohne Änderungen an den Kunden-Workloads angeboten. Außerdem werde ea auch keine weiteren Änderungen an den VM-Größen der HBv3-Serie geben.

Auf der Roadmap

AMD-Präsidentin Su hat schließlich ein paar Details zu den kommenden Epyc-Prozessoren verraten, die die Codenamen „Genoa“ und „Bergamo“ tragen.

„Genoa" werde voraussichtlich der weltweit leistungsstärkste Prozessor für General Purpose Computing sein. Entwickelt wir er mit bis zu 96 „Zen 4“-Kernen, die in 5-Nanometer-Technologie gefertigt werden, und mit DDR5 und PCIe 5 die nächste Generation von Speicher- und E/A-Technologien unterstützen.

Außerdem soll die CPU auch CXL unterstützen, was erhebliche Speichererweiterungsmöglichkeiten für Rechenzentrumsanwendungen ermöglicht. Geplant ist, dass „Genoa“ bereits 2022 produziert und auf den Markt gebracht wird.

„Bergamo" soll eine CPU, die insbesondere Cloud-native Anwendungen unterstützt. Laut Su soll sie über 128 „Zen 4c“-Kerne verfügen. Diese Kerne sind softwarekompatibel mit „Zen 4“ konzipiert und optimiert, um Konfigurationen mit höherer Kernzahl für Cloud-native Workloads zu ermöglichen, die von einer maximalen Thread-Dichte profitieren.

Außerdem zielt das Kerndesign auf eine erhöhte Energie-Effizienz und verspricht „bahnbrechender Leistung pro Sockel“. Der Prozessor soll trotzdem die gleichen Software- und Sicherheitsfunktionen wie Genua haben und sockelkompatibel sein. Bergamo wird voraussichtlich in der ersten Hälfte des Jahres 2023 auf den Markt kommen.

(ID:47783626)

:quality(80)/p7i.vogel.de/wcms/33/de/33de1ab85f5087fdb0ec4413d51d2dcd/0130981881v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/cf/d4/cfd4d42c78b625a00db0b727cdb7962b/0131030883v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/4c/3f/4c3f7e2bd17787c3cd16a871611af16f/0130591319v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/78/3d/783d67de6135df94a68299d87a12a74e/0130942387v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/23/5a/235a7cc8f0f6ee6992d706dd2422bb1f/0130911332v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/fd/a1/fda14c3b1c1b26538a1d36ea06c717e9/0130669567v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/30/eb/30eb9324ea3126096eb3a2ef820a8be5/0130704464v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/e4/d9e4f7b94025360fa28245bfccc07ada/0130927746v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ad/ec/adec05b770cd908c372d6641faf88fa1/0130765706v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f4/5b/f45bcf8db2cc67b07fd0378cc3300f4f/0130884384v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/ff/42ff4fc17a11a3fa7065cefc168ef25d/0130824377v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/63/c4/63c4700dcf2d980c5a5c4ed41890c62b/0130812458v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/4d/ac4d77a2d88556f01607b93d63a25f3e/0130721386v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a7/78/a778073f09b71e34b258aadcc396f100/0130856536v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ad/e9/ade9d0a11085d64eaaacbe51d683beca/0130726498v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/b3/e7b349f9bb427752fd3f4ae4c52c957d/0130852653v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/81/b3/81b359118a0e0e395cdebbddcfa03243/0130668020v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/41/ec/41ecbc8077275d54daf5895ae6f98b6c/0130998245v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/7c/6a/7c6ab6abcf322a0d07628261625577cc/0130815008v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/73/62/7362883dfa5efc0dcacb2e148a5dd7e0/0130738599v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ae/f9/aef9cef6337f8d1593202170a319e812/0130764658v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/49/7a/497af014bb9c80eb964cbd4b170f1af6/0130709118v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/8a/ba/8abadeb121d645fdb8fb5a68d6a4c9b8/0130541481v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d8/da/d8da211182a622032f94c6df22a902d0/0131020342v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/2d/9b/2d9bcbf76df4db8486e544d0a3b3e3e2/0130992530v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ee/0d/ee0d01ec7c94a6030ea13872c3adf768/0130913216v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/04/e1043ed6ca566979642a98b7dbadf235/0130912330v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f3/da/f3dacd38e5834ae3f3c9d0a4bc9664d3/0113348475.jpeg)

:quality(80)/p7i.vogel.de/wcms/90/f5/90f56ec6cb3ddbdabca2162fd5477836/0113078524.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/09/0f097990002b7600075e43c92af4a3fd/0110524571.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/ae/66ae9e32738784b57e2ad8c1a4b0986f/0109756744.jpeg)

:quality(80)/p7i.vogel.de/wcms/00/24/0024808d38d25431ae2719d3f8252908/0130726727v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/21/1c/211c24358dafb0b5433509e917e532b3/0130567036v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ee/3f/ee3f063b82737f0369c09ba7854587b5/0127234708v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f1/f0/f1f007a4518fa65d3cb0ea5ca465142a/0121300054v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/a8/28/a828f76369267628d833a12c26dd6579/0121131534v3.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/68/2d/682dd583dcc4c/fsas-afc-horizontal-2-positive-rgb-nov24.png)

:fill(fff,0)/p7i.vogel.de/companies/60/2a/602a8645d40e9/200226---derz-logo.jpg)

:quality(80)/images.vogel.de/vogelonline/bdb/1900300/1900364/original.jpg)

:quality(80)/images.vogel.de/vogelonline/bdb/1900300/1900365/original.jpg)

:quality(80)/images.vogel.de/vogelonline/bdb/1900300/1900366/original.jpg)

:quality(80)/p7i.vogel.de/wcms/2a/4d/2a4dc3648b0a80ad69faed0697837351/0125749477v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f6/e0/f6e0a44df4ca84f035752117c22e044b/0125232182v1.jpeg)