CPU-Tuning Was Sie über Gleitkomma-Berechnungen wissen sollten

DSPs, GPUs und FPGAs dienen als Beschleuniger für viele CPUs und bieten Vorteile bei Performance und Energie-Effizienz. Doch wie lässt sich die Performance von DSP-, GPU- und FPGA-Architekturen auf Basis ihrer FLOPS-Werte vergleichen? Altera gibt Auskunft.

Anbieter zum Thema

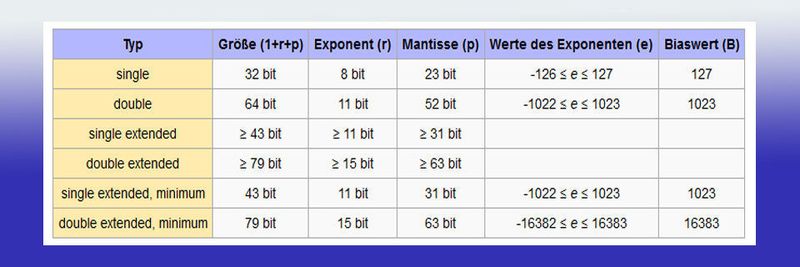

Bei der Vielzahl vorhandener Rechenarchitekturen benötigen Entwickler eine einheitliche Methode zum Vergleich dieser beiden Werte. Üblich ist die Messung der Gleitkomma-Operationen pro Sekunde (FLOPs; Floating-Point Operations per Second), wobei ein FLOP als Addition oder Multiplikation einer Zahl mit einfacher (Single 32-Bit) oder doppelter (Double 64-Bit) Genauigkeit entsprechend des Standards IEEE 754 definiert ist.

Alle höhergeordneten Funktionen wie Division, Quadratwurzel und Trigonometrie lassen sich aus Addierern und Multiplizierern erstellen. Da diese Operatoren und andere gängige Funktionen wie die Fast-Fourier-Transformation (FFT) und Matrix-Operatoren sowohl Addierer als auch Multiplizierer erfordern, besteht in allen diesen Architekturen häufig ein Verhältnis von 1:1 zwischen beiden.

Wie lässt sich nun die Performance von DSP-, GPU- und FPGA-Architekturen auf Basis ihrer FLOPS-Werte vergleichen? Der FLOPS-Spitzenwert wird durch Multiplikation der Summe von Addierern und Mulitplizierern mit der maximalen Betriebsfrequenz berechnet. Damit ergibt sich der theoretische Grenzwert für Berechnungen.

Dieser wird in der Praxis nie erreicht, da es generell nicht möglich ist, Algorithmen so zu implementieren, dass sie alle Recheneinheiten gleichzeitig beschäftigen. Die Zahl bietet jedoch einen guten Anhaltspunkt für Vergleiche.

DSP TMS320C667x und Tesla K20

Betrachten wir zuerst die DSP-GFLOPS-Performance. Dazu wurde ein DSP von Texas Instruments gewählt: der „TMS320C667x“. Er enthält acht DSP Cores, wobei jeder Core über zwei Verarbeitungs-Subsysteme verfügt.

Jedes Subsystem enthält vier Single-Precision Gleitkomma-Addierer und vier Single-Precision Gleitkomma-Multiplizierer. Dies entspricht insgesamt 64 Addierern und 64 Multiplizierern. Die schnellste Version läuft mit 1,25 GHz und bietet somit maximal 160 GFLOPs (siehe: Abbildung 1).

GPUs sind äußerst beliebte Bausteine – vor allem für die Bildverarbeitung. Einer der leistungsfähigsten ist „Nvidia Tesla K20“. Der Baustein basiert auf „CUDA“ Cores, die jeweils aus einer Single-Gleitkomma Multiplizier-/Addier-Einheit bestehen. Sie führt pro Taktzyklus in Single-Precision Gleitkomma-Konfiguration aus. In jeder Streaming Multiprocessor (SMX) Processing Engine finden sich 192 CUDA Cores.

Der K20 enthält derzeit 15 SMX, obwohl nur 13 zur Verfügung stehen (aufgrund der Prozessausbeute). Damit stehen insgesamt 2496 CUDA Cores zur Verfügung (mit 2 FLOPs pro Taktzyklus), die mit maximal 706 MHz betrieben werden. Die Single-Precision Gleitkomma-Performance beträgt damit insgesamt 3520 GFLOPs (siehe: Abbildung 2).

Die Gleitkomma-Engine

FPGA-Anbieter wie Altera bieten in ihren Bausteinen nun Gleitkomma-Engines in Hardware. Ein Single-Precision Gleitkomma-Multiplizierer und -Addierer wurde in die Hard-DSP-Blöcke der programmierbaren Logikstruktur integriert. Ein mittelgroßer FPGA der Altera FPGA-Serie Midrange Arria 10 ist der 10AX066. Er bietet 1678 DSP-Blöcke, von denen jeder 2 FLOPs pro Taktzyklus bereitstellt, was insgesamt 3376 FLOPs pro Taktzyklus ergibt.

Bei einer Taktfrequenz von 450 MHz (für Gleitkomma; die Festkomma-Modi sind höher) stehen somit 1520 GFLOPs bereit. Über eine ähnliche Berechnung kommt Altera auf 10.000 GFLOPs oder 10 TeraFLOPs Single-Precision-Performance bei den „FPGAs Highend Stratix 10“. Dies wird durch eine Kombination aus höherer Taktrate und größeren Bausteinen mit wesentlich mehr DSP-Rechenressourcen erzielt (siehe: Abbildung 3).

(ID:43625310)

:quality(80)/p7i.vogel.de/wcms/b7/51/b7517d2828afce2eed6c60c8f4b15e08/0131193094v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/a0/74/a074b1b682c5af4985ac6db2f521efcd/0131131347v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/a5/db/a5db7775305378d9d405e13e60f5e2f8/0130996707v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/59/c1/59c1cf46aaae9b03d58eb5d1711fbef3/0131024819v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/2a/c3/2ac3b65699dffc6bc3d44838b4a27223/0131131326v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/33/de/33de1ab85f5087fdb0ec4413d51d2dcd/0130981881v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/fc/91/fc91634cab380f053be693356d88ab11/0131193486v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/89/97/899791db276100161ea76f79dd649245/0131131469v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/03/53/03531922dce111ec6fa5b65684d9ea1c/0131055174v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/fd/a1/fda14c3b1c1b26538a1d36ea06c717e9/0130669567v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f4/5b/f45bcf8db2cc67b07fd0378cc3300f4f/0130884384v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/ff/42ff4fc17a11a3fa7065cefc168ef25d/0130824377v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/63/c4/63c4700dcf2d980c5a5c4ed41890c62b/0130812458v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/4d/ac4d77a2d88556f01607b93d63a25f3e/0130721386v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a7/78/a778073f09b71e34b258aadcc396f100/0130856536v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ad/e9/ade9d0a11085d64eaaacbe51d683beca/0130726498v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/b3/e7b349f9bb427752fd3f4ae4c52c957d/0130852653v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/81/b3/81b359118a0e0e395cdebbddcfa03243/0130668020v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/b8/26/b82629c5b95d15047e5489328a63a6e0/0131192769v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/17/94/179447f80cab81cfdbadd85c46cc9b72/0131191448v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/41/ec/41ecbc8077275d54daf5895ae6f98b6c/0130998245v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/e4/d9e4f7b94025360fa28245bfccc07ada/0130927746v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ae/f9/aef9cef6337f8d1593202170a319e812/0130764658v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/49/7a/497af014bb9c80eb964cbd4b170f1af6/0130709118v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/8a/ba/8abadeb121d645fdb8fb5a68d6a4c9b8/0130541481v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f1/ec/f1ec747ce9d298900249b7e29b123739/0131038591v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/ee/35ee684ecf7d82adb1b5360b04801c8d/0131008543v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/d8/da/d8da211182a622032f94c6df22a902d0/0131020342v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/2d/9b/2d9bcbf76df4db8486e544d0a3b3e3e2/0130992530v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f3/da/f3dacd38e5834ae3f3c9d0a4bc9664d3/0113348475.jpeg)

:quality(80)/p7i.vogel.de/wcms/90/f5/90f56ec6cb3ddbdabca2162fd5477836/0113078524.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/09/0f097990002b7600075e43c92af4a3fd/0110524571.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/ae/66ae9e32738784b57e2ad8c1a4b0986f/0109756744.jpeg)

:quality(80)/p7i.vogel.de/wcms/00/24/0024808d38d25431ae2719d3f8252908/0130726727v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/21/1c/211c24358dafb0b5433509e917e532b3/0130567036v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ee/3f/ee3f063b82737f0369c09ba7854587b5/0127234708v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f1/f0/f1f007a4518fa65d3cb0ea5ca465142a/0121300054v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/a8/28/a828f76369267628d833a12c26dd6579/0121131534v3.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/67/92/67921e1a932db/logo-pqplus---rgb.jpeg)

:quality(80)/images.vogel.de/vogelonline/bdb/927300/927325/original.jpg)

:quality(80)/images.vogel.de/vogelonline/bdb/927300/927326/original.jpg)

:quality(80)/images.vogel.de/vogelonline/bdb/927300/927331/original.jpg)

:quality(80)/images.vogel.de/vogelonline/bdb/927300/927330/original.jpg)

:quality(80)/p7i.vogel.de/wcms/7c/7e/7c7e2a8d36d8d6324ab2f03042052571/0129070776v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/e8/e7e8b85b5b149134e659fe1e6f6a49c2/0125147881v2.jpeg)