Deutlich mehr Leistung und geringerer Stromverbrauch IBM entwickelt 5-Nanometer-Chip

Wer 16-Nanometer-Chips verbaut, ist auf der Höhe der Zeit, zehn Nanometer sind das feinste, sieben noch gar nicht produktionsreif. Aber IBM-Forscher haben schon mal bewiesen, dass es auch nur fünf Nanometer sein können.

Anbieter zum Thema

Keine zwei Wochen vor der nächsten Supercomputer-Konferenz macht IBM mit einer Meldung auf sich aufmerksam, die nicht nur in dieses Feld passt. Zusammen mit den Partnern Globalfoundries und Samsung haben IBM-Forscher den Prozess für den Bau eines so genannten Nanosheet-Transistors auf Silizium-Basis mit fünf Nanometer (Nm) Strukturbreite in den Griff bekommen.

Vor nicht einmal zwei Jahren waren sieben Nanometer die Spitze

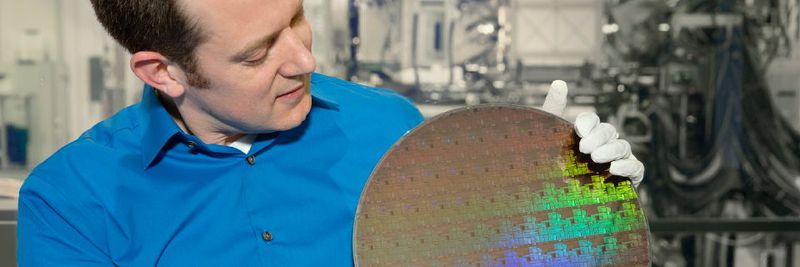

Vor nicht einmal zwei Jahren hat IBM die ersten Chips mit sieben Nanometern vorgestellt. Die tragen auf der Fläche eines Fingernagels 20 Milliarden Transistoren. Noch hat Big Blue die Produktionseinrichtungen für diesen Chip nicht fertig. Derweil habe Forscher im Testlabor die ersten Wafer mit Chips in Fünf-Nanometer-Technik hergestellt. Die haben auf gleicher Fläche dann gleich 30 Milliarden Switches.

Das bringt eine ganze Menge mehr Rechenpower. Die steigt zwar nicht analog zur höheren Transistordichte, sorgt laut IBM aber immerhin für 40 Prozent mehr Leistung. Bei gleicher Auslastung soll der enger gepackte Chip jedoch sogar 85 Prozent weniger Strom verbrauchen. Kürzere Schaltwege machen es möglich.Damit könnte der Chip nicht nur für stromfressende Superrechner interessant sein, sondern auch für die Verwendung in Smartphones und anderen mobilen Geräten, deren Akkus dann länger durchhalten würden.

Mit heute üblicher Technologie nicht möglich

Die Herstellung des neuen Chips gelang mit Extreme Ultraviolet (EUV) Lithografie, wie auch schon bei den 78-Nm-Chips. Dieses Verfahren erlaubt eine Feinabstimmung zwischen Performance und Leistungsaufnahme für ausgewählte Schaltkreise. Die Justierung resultiert in so genannten Nanosheet-Transistoren.

Fünf Nanometer Strukturbreite ließen sich im Prinzip auch mit der gängigen FinFET-Architektur erreichen, bei der gelegentlich etwas übertrieben von 3D-Chips die Rede ist. Theoretisch ließen sich die Abstände zwischen den stromführenden Fins verkleinern. Allerdings ist die Höhe der Fins limitiert, denn ein höherer Stromdurchfluss ist nicht möglich.

Nach IBM-Angaben sollen Chips mit 5-Nm-Strukurbreite „in nicht allzu ferner Zukunft in Produktion gehen“. Derzeit ist das Unternehmen aber noch damit beschäftigt, in seinem Fab 8 die Fertigungsprozesse für den 7-Nm-Chip einzurichten. Diese sollen 2018 auf den Markt kommen. Der jetzige Durchbruch in den Labors ist ein Ergebnis des 2014 angekündigten und auf fünf Jahre ausgelegten Programms, mit dem IBM drei Milliarden Dollar in die Erforschung neuartiger Chipstechnologien investiert.

(ID:44729683)

:quality(80)/p7i.vogel.de/wcms/cf/d4/cfd4d42c78b625a00db0b727cdb7962b/0131030883v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/4c/3f/4c3f7e2bd17787c3cd16a871611af16f/0130591319v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/78/3d/783d67de6135df94a68299d87a12a74e/0130942387v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/7c/52/7c5227112fa05f60e21a5880ef9e5b6b/0130929467v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/23/5a/235a7cc8f0f6ee6992d706dd2422bb1f/0130911332v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/49/7a/497af014bb9c80eb964cbd4b170f1af6/0130709118v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/fd/a1/fda14c3b1c1b26538a1d36ea06c717e9/0130669567v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/30/eb/30eb9324ea3126096eb3a2ef820a8be5/0130704464v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/e4/d9e4f7b94025360fa28245bfccc07ada/0130927746v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ad/ec/adec05b770cd908c372d6641faf88fa1/0130765706v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f4/5b/f45bcf8db2cc67b07fd0378cc3300f4f/0130884384v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/42/ff/42ff4fc17a11a3fa7065cefc168ef25d/0130824377v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/63/c4/63c4700dcf2d980c5a5c4ed41890c62b/0130812458v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/4d/ac4d77a2d88556f01607b93d63a25f3e/0130721386v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a7/78/a778073f09b71e34b258aadcc396f100/0130856536v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ad/e9/ade9d0a11085d64eaaacbe51d683beca/0130726498v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/b3/e7b349f9bb427752fd3f4ae4c52c957d/0130852653v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/81/b3/81b359118a0e0e395cdebbddcfa03243/0130668020v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/41/ec/41ecbc8077275d54daf5895ae6f98b6c/0130998245v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/7c/6a/7c6ab6abcf322a0d07628261625577cc/0130815008v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/73/62/7362883dfa5efc0dcacb2e148a5dd7e0/0130738599v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ae/f9/aef9cef6337f8d1593202170a319e812/0130764658v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/8a/ba/8abadeb121d645fdb8fb5a68d6a4c9b8/0130541481v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ee/0d/ee0d01ec7c94a6030ea13872c3adf768/0130913216v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/04/e1043ed6ca566979642a98b7dbadf235/0130912330v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/c4/43/c44345288e65c7a41cd5ce0da355ba1f/0130874335v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/0c/b6/0cb659b857a730ab94b3641fb3932da5/0130793406v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f3/da/f3dacd38e5834ae3f3c9d0a4bc9664d3/0113348475.jpeg)

:quality(80)/p7i.vogel.de/wcms/90/f5/90f56ec6cb3ddbdabca2162fd5477836/0113078524.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/09/0f097990002b7600075e43c92af4a3fd/0110524571.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/ae/66ae9e32738784b57e2ad8c1a4b0986f/0109756744.jpeg)

:quality(80)/p7i.vogel.de/wcms/00/24/0024808d38d25431ae2719d3f8252908/0130726727v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/21/1c/211c24358dafb0b5433509e917e532b3/0130567036v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ee/3f/ee3f063b82737f0369c09ba7854587b5/0127234708v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f1/f0/f1f007a4518fa65d3cb0ea5ca465142a/0121300054v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/a8/28/a828f76369267628d833a12c26dd6579/0121131534v3.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/62/0b/620b6080ee47f/dtmlogo.png)

:fill(fff,0)/p7i.vogel.de/companies/64/39/6439b8923f905/vzm-logo-2023-rgb-400pxb-it-sicherheit.png)

:quality(80)/p7i.vogel.de/wcms/fb/5f/fb5f1d119682e3623cd9fff5fa80b244/0129756328v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ad/e9/ade9d0a11085d64eaaacbe51d683beca/0130726498v1.jpeg)