UHD-FO, EMIB, CoWoS und RDL Die Topspieler in der Branche für Hochleistungs-Aufbau- und Verbindungstechnik

High Performance Computing treibt das Wachstum der Hochleistungs-Aufbau- und ‑Verbindungstechnik an und es sind mehrere Plattformen für neue Technologien erforderlich. Das gehört zu den Ergebnissen der jüngsten Untersuchung vom Marktforschungs- und Strategieberatungsunternehmen Yole Développement (Yole) zur Hochleistungs-Aufbau- und ‑Verbindungstechnik.

Anbieter zum Thema

Wie die Prognose der Yole-Studie „High-End Performance Packaging 2022 – Focus on 2.5D/3D Integration“ lautet, wird die Hochleistungs-Aufbau- und ‑Verbindungstechnik bis zum Jahr 2027 zu einem Marktwert von 7,87 Milliarden Dollar werden bei einem durchschnittlichen Wachstum 19 Prozent. Dabei sollen UHD-FO (Ultra High-Density Fan-Out), HBM, 3 DS und aktive Silizium-4‑Interposer in fünf Jahren mehr als 50 Prozent des Marktes für die Hochleistungs-Aufbau- und ‑Verbindungstechnik ausmachen.

Yole veröffentlicht das ganze Jahr über Analysen, einschließlich Technologie- und Marktberichten, vierteljährlichen Marktmonitoren und Abbauanalysen. Die gestern veröffentlichte mit einem Preis von Studie analysiert detailliert die Herausforderungen und Chancen im Markt mit Hochleistungs-Aufbau- und ‑Verbindungstechnik. Sie bietet Marktdaten zu wichtigen Technologien sowie Informationen über Wertschöpfungskette, Infrastruktur und Wettbewerbslandschaft.

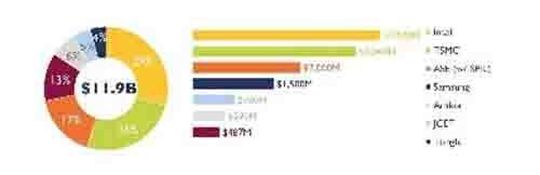

Stefan Chitoraga, Technologie- und Marktanalyst für Aufbau- und Verbindungstechnik sowie Montage bei Yole, bemerkt: „2021 investierten die wichtigsten Player etwa 11,6 Milliarden Dollar in Aktivitäten zur Aufbau- und Verbindungstechnik. Sie wissen, wie wichtig es ist, gegen eine Verlangsamung des Mooreschen Gesetzes anzukämpfen, und passen ihre Strategien in dieser Richtung an.“

Die Gewinner und Verlierer

Intel ist mit 3,5 Milliarden der wichtigste Investor. Seine 3‑D‑Chipstapeltechnologie beziechnet das Unternehmen mit „Foveros“. Sie besteht darin, Dies auf einem aktiven Silizium-Interposer zu stapeln. Die 2,5‑D-Lösung für die Aufbau- und Verbindungstechnik ist eine EMIB (Embedded Multi-Die Interconnect Bridge), die einen 55-μm-Bump-Pitch nutzt. Die Kombination von Foveros und EMIB5 führt zur „Co-EMIB“, die für die GPU „Ponte Vecchio“ verwendet wird. Intel plant, für Foveros Direct eine Hybrid-Bonding-Technologie anzuwenden.

Der zweitplatzierte, TSMC, folgt mit einer Investition von 3,05 Milliarden Dollar. TSMC sichert sich mit seinen „InFO8“‑Produkten (Integrierte Fan-Out) mehr Geschäft für UHD‑FO und definiert neue Pläne auf Systemebene und Technologie für 3D‑SoC (System on an Chip). Seine „CoWoS“‑Plattform (Chip-on-Wafer-on-Substrate) bietet Lösungen wie „RDL“ (Re-Distribution Layer, Umverdrahtungsebene) und Silizium-Interposer, während seine „LSI“‑Plattform ein direkter Konkurrent für EMIB ist. TSMC hat sich als Zugpferd der Hochleistungs-Aufbau- und ‑Verbindungstechnik mit führenden fortschrittlichen „Front-End“‑Knoten hervorgetan, die es ihm ermöglichen, die Aufbau- und Verbindungstechnik der nächsten Generation auf Systemebene zu dominieren.

An dritter Stelle steht mit einer geschätzten Investition von 2 Milliarden Dollar ASE als größtes und einziges Outsourced Semiconductor Assembly and Test, externe Halbleiterhersteller- und ‑testunternehmen (OSAT), das versucht, mit den Foundries und Integrated Device Manufacturer (IDM) in der Aufbau- und Verbindungstechnik in Wettbewerb zu stehen. Mit seinem FoCoS‑Produkt (Fan Out Chip on Substrate) ist ASE derzeit auch das einzige OSAT mit einer UHD‑Fan-Out-Technik.

Derzeit besitzen OSAT nicht die finanziellen und Front-End-Möglichkeiten, um im Rennen um die fortschrittliche Aufbau- und Verbindungstechnik mit den großen Playern wie Intel, TSMC und Samsung Schritt zu halten.

Die Analysten von Yole identifizierten auch Samsung direkt hinter ASE. Samsung hat seine „I‑Cube“-Technologie, die der „CoWoS-S“ ähnelt. Samsung ist einer der Marktführer bei 3‑D-gestapelten Speicherlösungen und bietet HBM und 3DS. Sein „X‑Cube“ wird Hybrid-Bonding-Verbindungen nutzen.

(ID:48086679)

:quality(80)/p7i.vogel.de/wcms/b0/c2/b0c21d87e3f49ebddfc5eb3e6eb1ace7/0130275831v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/02/4b/024b20f0970c75df608278d9fe5b29f2/0130254181v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/af/d6/afd6a823c663c6263f9d00b4e2a93e36/0130258811v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/11/1b/111bc87a5d1dbfad099d7b45a6070d4c/0130235056v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/40/1d/401d49f8d11d5271136097b0958e81d5/0130262496v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/09/18/0918fa09263a95f290813814e683b5a5/0130382915v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/56/6f/566f5bb411bbc978e2f3174053ed0d77/0130027496v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/f7/eff79ff9cc8ace73c0da4e4f8d8c7a11/0130192849v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f5/49/f5498274c07b00bcdc104630b6df47de/0130252727v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/55/fe/55fe30fb3e4238e2da3996ee30316f7a/0130004524v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/54/69/5469ac4ce69d115dc6d6a4428b950932/0130145481v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/55/4e/554ebc23f1c789a28a798218f29c062d/0130169882v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/1b/31/1b3171cb6022332e381053024a22fb1f/0130115845v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/d1/28/d1281144c2f6e55ef6fdb0e933fe0845/0130354631v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/d0/2ed0a62794a9e6fe853196818b3cb51f/0130353302v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e3/2a/e32a293cf06836748e90d497ba32fb93/0130347695v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ff/37/ff374ad35adb0b63ea735878334d3ef1/0130236761v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6e/d7/6ed78cab09dfcd389cd7ab7f5659886a/0130054146v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/b9/65/b9654dfbc8d07f61e35ef56044100f08/0130039376v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ab/2f/ab2fe34a407574104b8542b1547f0057/0129966653v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/9b/bf/9bbf759deadf4ca1d6310f7cbdbff980/0129915890v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/b3/00/b300e9067fa49df042de85fe1554b969/0130369559v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/00/23/00232dc2c4ae51128b5e0881aeb0908b/0130233561v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/5c/1e/5c1e606e8d54467bc29043a16a344dd7/0130157161v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/4a/99/4a99d1e657e57f8d586cc19e60b1824f/0130060276v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/63/1f/631f96e15c822a8a5c91de8ca4b8ab0e/0130142087v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/be/ab/beabe1c9a580ab042d4833bcae39cf7d/0130435287v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/c5/c9/c5c97bb528833380fcd3b869da91e30c/0130421413v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/35/91/3591c134a56d4b774f8a34f3e64e0e56/0130358795v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/9d/d8/9dd86b0d06f1130a37a805b1ad15d90f/0130301130v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f3/da/f3dacd38e5834ae3f3c9d0a4bc9664d3/0113348475.jpeg)

:quality(80)/p7i.vogel.de/wcms/90/f5/90f56ec6cb3ddbdabca2162fd5477836/0113078524.jpeg)

:quality(80)/p7i.vogel.de/wcms/0f/09/0f097990002b7600075e43c92af4a3fd/0110524571.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/ae/66ae9e32738784b57e2ad8c1a4b0986f/0109756744.jpeg)

:quality(80)/p7i.vogel.de/wcms/17/ab/17ab3338f508225455c868356603ca19/0130105849v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/0a/50/0a5048fd61449f264fd6ba611bb5ec83/0130044632v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ee/3f/ee3f063b82737f0369c09ba7854587b5/0127234708v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f1/f0/f1f007a4518fa65d3cb0ea5ca465142a/0121300054v3.jpeg)

:quality(80)/p7i.vogel.de/wcms/a8/28/a828f76369267628d833a12c26dd6579/0121131534v3.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/5f/74/5f7479b1443af/panduit-logo2015-bp-below-aligned-tm.jpg)

:fill(fff,0)/p7i.vogel.de/companies/64/e4/64e4be0db6ddc/rittal-4c-w.png)

:fill(fff,0)/p7i.vogel.de/companies/68/2d/682dd583dcc4c/fsas-afc-horizontal-2-positive-rgb-nov24.png)

:quality(80)/p7i.vogel.de/wcms/c2/62/c262b34c46d646db2ddce3a018e41dce/0130051138v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/3d/cc3d4fe3b9fe5791e9cbf6c6ab2240b8/0127067182v1.jpeg)